IBM avslöjar Telum II-arkitektur och Spyre Accelerator på Hot Chips 2024.

IBM har avslöjat arkitekturdetaljerna för sin kommande IBM Telum II-processor och IBM Spyre Accelerator vid Hot Chips 2024-konferensen. Dessa nya teknologier är designade för att avsevärt skala bearbetningskapaciteten över nästa generations IBM Z stordatorsystem, vilket möjliggör acceleration av både traditionella AI-modeller och stora AI-modeller genom en ny ensemblemetod för AI. Eftersom många generativa AI-projekt som utnyttjar stora språkmodeller (LLM) övergår från proof-of-concept till produktion, har företagens efterfrågan på energieffektiva, säkra och skalbara lösningar blivit en högsta prioritet.

Enligt Morgan Stanleys forskning förväntas effektbehovet för generativ AI öka med 75 % årligen under de kommande åren, med prognoser som indikerar att AI:s energiförbrukning kan matcha Spaniens 2026. Detta har drivit IBM-kunder att prioritera arkitektoniska beslut som stöder grundmodeller av lämplig storlek och hybridbaserade tillvägagångssätt för AI-arbetsbelastningar.

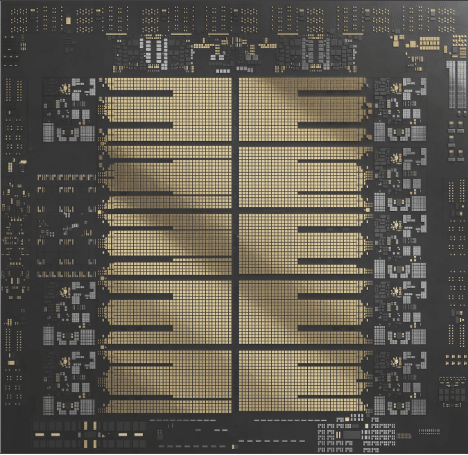

IBM Telum II-processorn är designad för att driva nästa generations IBM Z-system. Den har ökad frekvens, utökad minneskapacitet, 40 % tillväxt i cache och en integrerad AI-acceleratorkärna. Den nya processorn introducerar en sammanhängande ansluten Data Processing Unit (DPU) konstruerad för att accelerera komplexa IO-protokoll för nätverk och lagring på stordatorn. DPU:n förenklar systemdriften och förbättrar prestandan hos huvudkomponenterna, vilket gör Telum II-processorn väl lämpad för företagsdatorlösningar som stödjer LLM:er och branschens komplexa transaktionsbehov.

Som komplement till Telum II-processorn är IBM Spyre Accelerator, som ger ytterligare AI-beräkningsmöjligheter. Tillsammans bildar Telum II- och Spyre-chipsen en skalbar arkitektur som stöder ensemblemetoder för AI-modellering – som kombinerar flera maskininlärnings- eller djupinlärnings-AI-modeller med kodare LLM. Denna ensemblemetod utnyttjar styrkorna hos varje modellarkitektur för att leverera mer exakta och robusta resultat jämfört med enskilda modeller. IBM Spyre Accelerator, introducerad som en förhandsvisning på Hot Chips 2024, kommer att finnas tillgänglig som ett tilläggsalternativ. Den är fäst via en 75-watts PCIe-adapter och är skalbar för att passa kundens behov.

Tina Tarquinio, VP of Product Management för IBM Z och LinuxONE, betonade IBM:s engagemang för att ligga steget före tekniktrender, särskilt de eskalerande kraven på AI. Hon sa att Telum II-processorn och Spyre Accelerator är designade för att leverera högpresterande, säkra och energieffektiva företagsdatorlösningar. Dessa innovationer, som har utvecklats i flera år, kommer att introduceras i IBMs nästa generations IBM Z-plattform, vilket gör det möjligt för kunder att dra nytta av LLM och generativ AI i stor skala.

Telum II-processorn och IBM Spyre Accelerator kommer att tillverkas av IBMs mångåriga partner, Samsung Foundry, med hjälp av sin högpresterande, energieffektiva 5nm-processnod. Tillsammans kommer dessa teknologier att stödja en rad avancerade AI-drivna användningsfall utformade för att låsa upp affärsvärde och skapa nya konkurrensfördelar. Till exempel kan förbättrad bedrägeriupptäckt i hemförsäkringsanspråk uppnås genom ensemble AI-modeller som kombinerar LLM med traditionella neurala nätverk. Dessutom kan avancerad upptäckt av misstänkta finansiella aktiviteter hjälpa till att stödja efterlevnad av regulatoriska krav och minska risken för ekonomiska brott. Samtidigt kan AI-assistenter påskynda applikationernas livscykler, överföra kunskap och tillhandahålla kodförklaringar och transformationer.

Telum II-processorn kommer att ha åtta högpresterande kärnor som körs på 5.5 GHz, med 36 MB L2-cache per kärna och en 40 % ökning av chipets cachekapacitet, totalt 360 MB. Den virtuella nivå-4-cachen kommer att erbjuda 2.88 GB per processorlåda, en ökning med 40 % jämfört med föregående generation. Den integrerade AI-acceleratorn möjliggör AI-inferencing med låg latens och hög genomströmning i transaktioner, vilket ger en fyrfaldig ökning av beräkningskapaciteten per chip jämfört med den senaste generationen. Dessutom är den nya I/O Acceleration Unit DPU, integrerad i Telum II-chippet, designad för att förbättra datahanteringen med en 50 % ökning av I/O-densiteten, vilket förbättrar IBM Z:s totala effektivitet och skalbarhet för storskaliga AI-arbetsbelastningar och data -intensiva applikationer.

IBM Spyre Accelerator är en specialbyggd accelerator av företagsklass designad för att hantera komplexa AI-modeller och generativa AI-användningsfall. Den har upp till 1 TB minne, fördelat på åtta kort i en vanlig IO-låda, som stöder arbetsbelastningar för AI-modeller över stordatorn samtidigt som den inte förbrukar mer än 75W per kort. Varje chip har 32 beräkningskärnor som stöder int4, int8, fp8 och fp16 datatyper, vilket möjliggör både AI-applikationer med låg latens och hög genomströmning.

Telum II-processorn kommer att driva IBMs nästa generations IBM Z- och IBM LinuxONE-plattformar och kommer att finnas tillgänglig 2025. IBM Spyre Accelerator, som för närvarande är i teknisk förhandsvisning, förväntas vara tillgänglig 2025.

Engagera dig med StorageReview

Nyhetsbrev | Youtube | Podcast iTunes/Spotify | Instagram | Twitter | TikTok | Rssflöde