Marvell Structera completes interoperability testing with DDR4 and DDR5 solutions from Micron, Samsung, and SK hynix.

Marvell Technology has reinforced its leadership in the Compute Express Link (CXL) ecosystem by announcing that its Structera CXL memory-expansion controllers and near-memory compute accelerators have completed interoperability testing with DDR4 and DDR5 solutions from Micron, Samsung, and SK Hynix. This news builds on Marvell’s earlier validation with AMD EPYC processors and 5th Gen Intel Xeon Scalable platforms, establishing Structera as the only CXL 2.0 portfolio with validated interoperability across all major CPU architectures and the top three memory suppliers.

For hyperscalers and cloud providers, this milestone is more than just another box to check. It indicates that Structera has reached a level of maturity that supports real-world deployment at scale.

The Need for Interoperability

Modern data-driven workloads, especially in AI, generative AI, and high-performance computing, place significant stress on memory systems. Memory is no longer just a passive component. Instead, it is a key performance enabler. The increasing use of CXL highlights the importance of interoperability and comprehensive ecosystem validation. By ensuring smooth operation across DDR generations, Structera lowers integration risk, simplifies qualification, and helps OEMs and cloud operators design systems that can adapt to supply chain changes while still meeting performance and efficiency targets.

Structera X 2504 Memory-Expansion Controller

| Features | Details |

|---|---|

| Standards and interfaces | • PCIe 5.0 (2.5/5.0/8.0/16.0/32.0 GT/s) • CXL 2.0 (8.0/16.0/32.0 GT/sec) • PCIe/CXL host interfaces • 16-lane physical interface (PHY) |

| CXL modes | • CXL 1.1 Exclusive Restricted CXL Device (eRCD) mode • Power-saving modes • Lane-reversal • Spread-spectrum clocking for common reference-clock links • QoS telemetry |

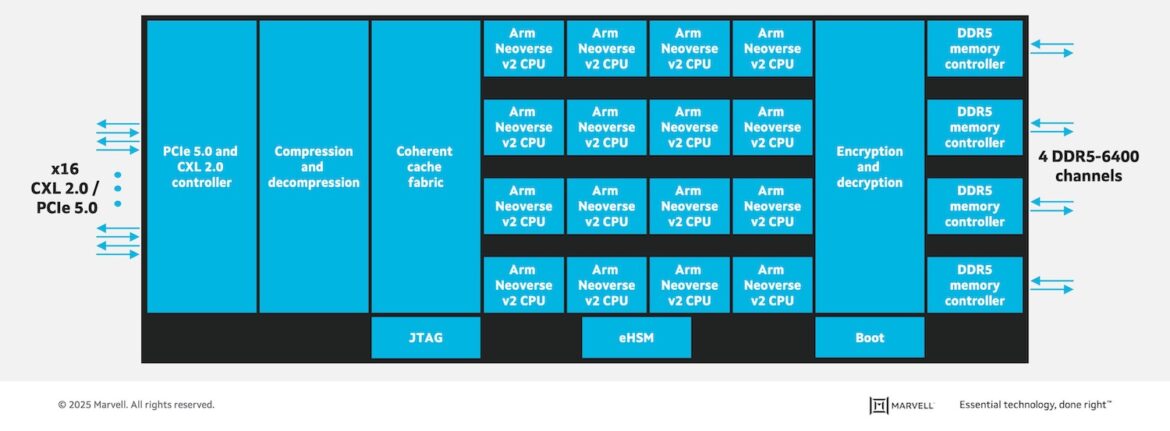

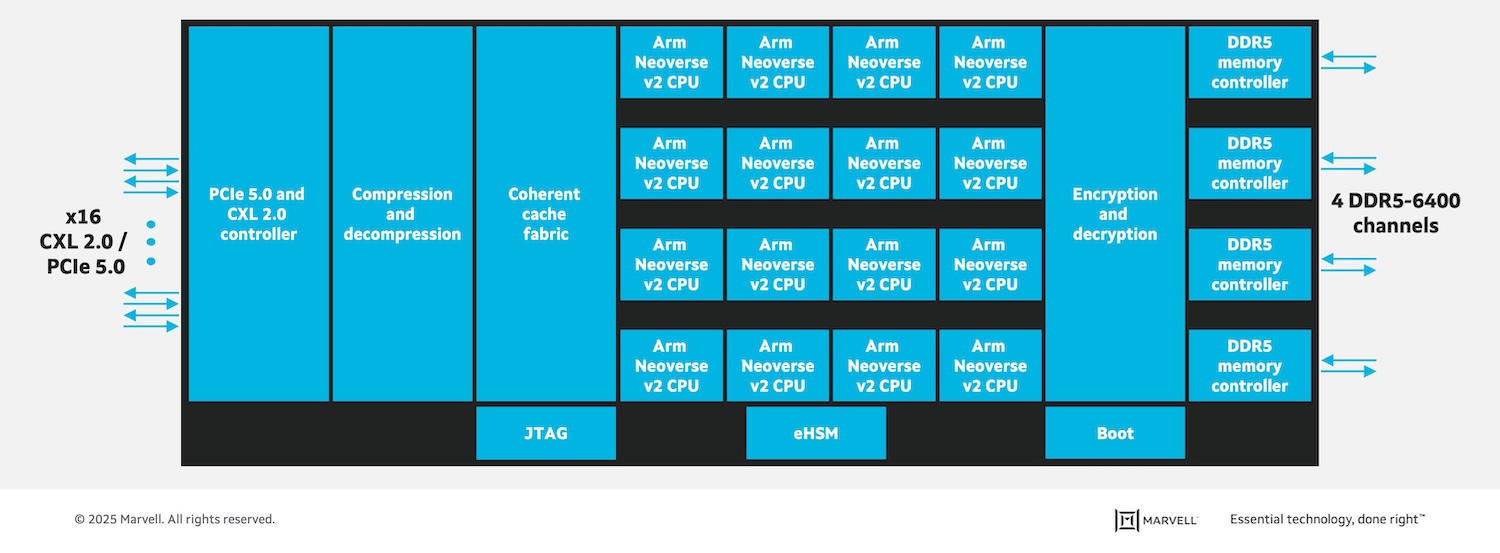

| CPU subsystem | • Based on Armv9.0-A and Armv8.5-A • High-performance out-of-order (OOO) architecture with 16 high-performance Arm® Neoverse V2 cores to reduce data movement and enhance parallelism • Highly efficient multilevel cache subsystem • Comprehensive security protection with embedded hardware-security module and secure boot via Arm TrustZone® • Hardware floating-point, SIMD, MMU, and virtualization capabilities • Secure operation with three privilege levels, ensuring isolation and compatibility within the Arm software ecosystem |

| Memory | • Support for DDR5: – Up to 6400 MT/s data rate – Subdivided into two 40-bit subchannels (32 data bits, eight ECC bits) – Up to four physical ranks per subchannel – U/R/LRDIMM and soldered DRAM – DRAM interfaces with enhanced RAS capabilities – MPAM support for bandwidth partitioning and monitoring – DRAM crypto with XTS-AES 256 on data with optional address scrambling |

| Control and management | • Miscellaneous I/O interfaces: SPI/QSPI/xSPI, GPIO, UART, I3C, TWSI, I2C/SMBus • Multiple embedded Arm Cortex M7 processors: – System-control processor (SCP) – Management-control processor (MCP) – Cryptographic-control processor (CCP) – PCIe configuration-offload processor (PCP) • Embedded hardware security module (eHSM) using Arm Cortex M3 processor • Extensive power and thermal management capabilities • Compatible with Arm Server Base System Architecture (SBSA) |

| Compression | • Support for four channels of DDR5-3200 at 100% bandwidth • Support for 4K or 1K page sizes • LZ4 algorithm support • Data integrity protection, including poison and decompress-after-compress |

| Package characteristics | • 35mm x 35mm package with 0.8 mm ball pitch |

Structera A 2504 Memory-Expansion Controller

| Features | Details |

|---|---|

| Standards and interfaces | • PCIe 5.0 (2.5/5.0/8.0/16.0/32.0 GT/s) • CXL 2.0 (8.0/16.0/32.0 GT/sec) • PCIe/CXL host interfaces • 16-lane physical interface (PHY) |

| CXL modes | • CXL 1.1 Exclusive Restricted CXL Device (eRCD) mode • Power-saving modes • Lane-reversal • Spread-spectrum clocking for common reference-clock links • QoS telemetry |

| Memory | • Support for DDR5: – Up to 6400 MT/s data rate – Subdivided into two 40-bit subchannels (32 data bits, eight ECC bits) – Up to four physical ranks per subchannel • U/R/LRDIMM and soldered DRAM • DRAM interfaces with enhanced RAS capabilities • MPAM support for bandwidth partitioning and monitoring • DRAM crypto with AES-XTS 256 on data with optional address scrambling |

| Control and management | • Miscellaneous I/O interfaces: SPI/QSPI/xSPI, GPIO, UART, I3C, TWSI, I2C/SMBus • Multiple embedded Arm Cortex M7 processors: – System-control processor (SCP) – Management-control processor (MCP) – Cryptographic-control processor (CCP) – PCIe configuration-offload processor (PCP) • Embedded hardware security module (eHSM) using Arm Cortex M3 processor • Extensive power and thermal management capabilities • Compatible with Arm Server Base System Architecture (SBSA) |

| Compression | • Support for 4K or 1K page sizes • LZ4 algorithm support • Data integrity protection, including poison and decompress-after-compress |

| Package characteristics | • 35mm x 35mm package with 0.8 mm ball pitch |

This level of interoperability ensures that cloud architects and infrastructure buyers have maximum configuration flexibility, allowing workload-specific tuning that wouldn’t be possible with a less mature solution.

Deployment Driven By Hyperscalers

Marvell has transformed interoperability from a mere technical requirement into a business advantage. Structera offers a flexible engagement model, enabling hyperscalers to tailor product configurations for various workloads, whether for standard deployments or highly customized solutions. This flexibility reduces qualification times and speeds up deployment in live environments where infrastructure agility is essential.

Meanwhile, Marvell offers Structera technology as silicon IP, paving the way for customers seeking deeper integration into custom SoCs or specialized accelerators. This method enables cloud and system providers to embed silicon-tested CXL functionality directly into their designs, resulting in improved performance per watt and cost efficiency, while ensuring compatibility with the broader CXL ecosystem.

Structera’s Impact

Industry partners highlight the importance of this interoperability milestone.

Praveen Vaidyanathan, Marvell VP and GM of Cloud Memory Products, noted that as AI and HPC workloads scale to hundreds of terabytes of memory, eliminating bottlenecks is crucial. He highlighted that Micron’s collaboration with Marvell focuses on building a scalable, high-efficiency CXL infrastructure that underpins AI advancements.

Uksong Kang, SK hynix Head of Next-Gen Product Planning, said the validation with Structera makes memory expansion more accessible and flexible, underscoring how it provides cloud operators with the confidence and tools to build future-ready architectures.

Together, these partnerships demonstrate strong alignment across the value chain, including memory vendors, CPU leaders, and Marvell, ensuring that CXL adoption faces fewer obstacles and provides greater predictability.

Structera Portfolio

Marvell’s Structera family targets two complementary use cases, each vital to next-generation cloud infrastructure:

- Structera A (Near-Memory Accelerators): Equipped with 16 Arm Neoverse V2 cores and multiple CXL-enabled memory channels, this platform is optimized for high-bandwidth workloads, such as deep learning recommendation models (DLRM), AI inference, and machine learning training.

- Structera X (Memory-Expansion Controllers): Designed for high-capacity, general-purpose workloads, these controllers scale server memory into the terabyte range, unlocking performance for applications such as in-memory databases, analytics, and AI pipelines.

Both device families are industry firsts in supporting four memory channels, integrating inline LZ4 compression, and leveraging advanced 5nm process technology, which together deliver the power efficiency and density that hyperscalers demand.

With Structera, Marvell has positioned itself at the center of the rapidly maturing CXL landscape. As hyperscalers, OEMs, and service providers seek scalable, efficiency-driven solutions to handle the growing data demands, Structera offers the rare combination of interoperability, flexibility, and ecosystem maturity that accelerates adoption and reduces deployment risk.

For those designing cloud-scale AI infrastructure or enabling next-generation enterprise workloads, Structera is shaping up to be not just a CXL product family but a foundation for the data centers of the future.

Engage with StorageReview

Newsletter | YouTube | Podcast iTunes/Spotify | Instagram | Twitter | TikTok | RSS Feed